服務熱線

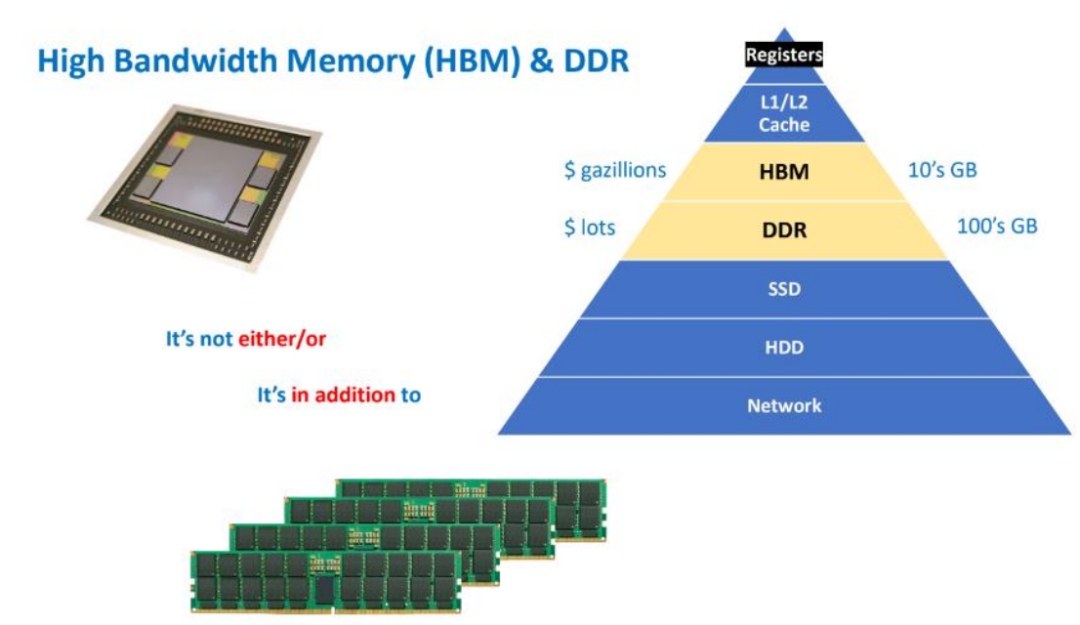

一、引言:AI時代的“內存革命”

在生成式AI、超算和高性能GPU的浪潮中,有一種看似低調卻決定算力上限的關鍵部件——HBM(High Bandwidth Memory,高帶寬內存)。

如果把GPU比作一臺擁有數萬氣缸的超高性能引擎,那么HBM就是為它提供燃料的“供油系統”。

油供不上,再好的引擎也只能空轉。HBM的使命,就是讓數據以“洪流”的速度流入GPU核心,而不是被“滴灌”。

二、HBM是什么:不是“芯片”,而是“系統級接口標準”

許多人以為HBM是一種新的內存芯片,其實更準確地說,HBM是一種定義了“如何讓DRAM以極高帶寬互連”的接口與封裝技術規范。

它不是在單顆芯片上堆性能,而是在“堆疊”和“互連”上下功夫。

一個完整的HBM模塊通常由:

多層垂直堆疊的 DRAM芯片(Die)(4層、8層、甚至12層); 內部貫穿每一層的 TSV(Through-Silicon Via,硅通孔); 以及連接GPU與HBM的 中介層(Interposer) 共同組成。

HBM的核心思路是:讓數據在最短路徑內穿越最多的并行通道。

傳統GDDR的思路是“跑得快”(高頻),HBM的思路是“路更多”(寬位寬)。結果是:單位時間傳輸量呈數量級提升。

三、GPU與HBM的關系:算力與供給的“饑餓游戲”

1. GPU的“胃口”

GPU(圖形處理器)天生是“并行怪獸”。

一顆如NVIDIA H100的GPU擁有18,432個CUDA核心,相當于上萬個小計算單元同時吃數據。

但問題是,這些核心吃得太快。如果內存送數據的速度跟不上,GPU就會“餓著”——

這就是所謂的內存瓶頸(Memory Bottleneck)。

2. 帶寬的定義與瓶頸

內存帶寬(Memory Bandwidth)表示單位時間內內存可傳輸的數據量。

計算公式:

帶寬(GB/s) = [總線位寬(bit) × 有效傳輸速率(GT/s)] ÷ 8

HBM的革命性突破在于:

位寬極寬

:每堆HBM的總線可達1024位甚至2048位; 傳輸頻率高

:每秒傳輸速率可達6.4GT/s以上; 距離極短、損耗極低

:得益于中介層互連。

結果就是:

HBM3E帶寬 ≈ 1.2 TB/s

GDDR6帶寬 ≈ 0.064 TB/s

也就是說,HBM的“供料速度”是GDDR的近20倍。

3. 為什么AI必須用HBM?

AI訓練和推理(尤其是大型語言模型、圖像生成模型)涉及數百GB到數TB的數據流。

這些數據要在GPU與內存之間不停來回傳遞:

參數 → 激活值 → 梯度 → 更新。

如果帶寬不夠,GPU核心就像賽車堵在加油站門口——算力再強也沒法發揮。

HBM的高帶寬和低延遲正是為了解決這種“算力饑餓”。

四、HBM的結構:從“平面走線”到“垂直通道”

1. 3D堆疊(Stack)

傳統DRAM是平鋪在PCB上的,而HBM將多顆DRAM芯片垂直堆疊,通過微凸塊(Microbump)層層互連。

這就像把存儲單元從“平面社區”變成“摩天大樓”,在相同面積下,容量和通道密度成倍增加。

2. 硅通孔(TSV)

每一層DRAM芯片內部鉆出直徑僅5-10微米的通孔,填入銅或鎢等導電材料。

這些通孔就是信號、電源、地線的垂直“電梯井”。

它們實現:

最短互連路徑(僅50~100微米);

最高互連密度(數萬通道);

最低信號延遲與功耗。

換句話說,TSV讓“樓層之間的數據”以幾乎無延遲的方式直達。

這就是HBM得以實現“超寬總線位寬”的硬件根基。

3. 中介層(Interposer)

GPU與HBM堆棧并不是直接焊在PCB上,而是共同安裝在一塊中介層上。

中介層是一塊超高密度布線的硅基基板(或高端有機基板),線寬/線距可達1μm級。

它的作用:

承載GPU和HBM; 提供超密互連橋梁,在毫米級距離內連接數千I/O信號; 保證信號完整性、低延遲、低功耗。

你可以把中介層想象成一塊“高架橋系統”,

GPU與HBM之間通過成千上萬條“微型高速公路”直連,信號幾乎不繞路、不打彎。

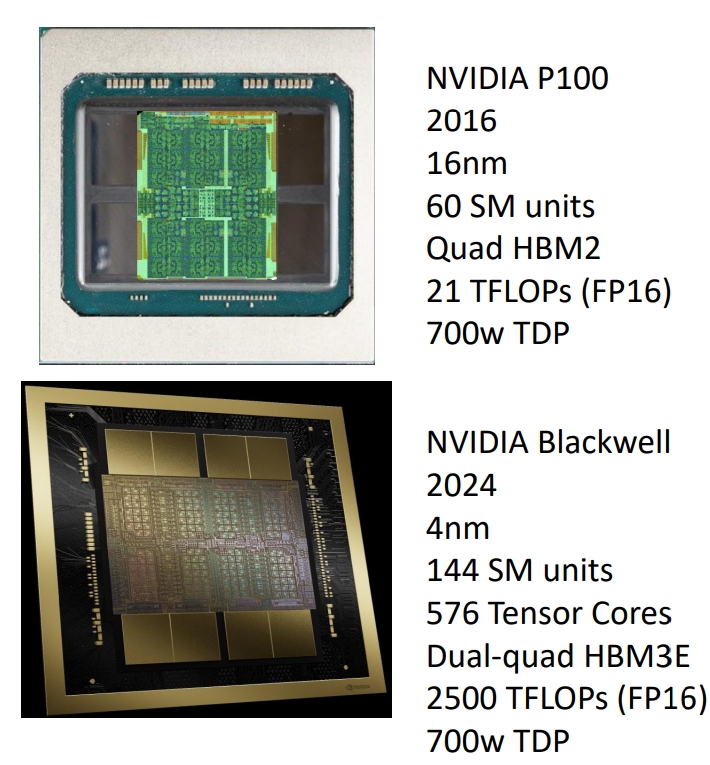

五、HBM的演進:從1代到4代的“極限競速”

代別 | 典型帶寬(每堆) | 數據速率 | 堆疊層數 | 狀態 |

HBM1 | ~128 GB/s | 1 Gbps | 4 | 已退役 |

HBM2 | ~256 GB/s | 2 Gbps | 8 | 主流 |

HBM2E | ~460 GB/s | 3.6 Gbps | 8 | AI訓練主力 |

HBM3 | ~819 GB/s | 6.4 Gbps | 12 | 高端AI應用 |

HBM3E | ~1225 GB/s | 9.2 Gbps | 12 | 2024-2025量產 |

HBM4 | >1500 GB/s | >12 Gbps | 16(預期) | 研發中 |

未來的HBM4正在朝著更高層數、更寬位寬、芯片直接集成(3D-SoIC)方向演進。

這意味著GPU與HBM的邊界將越來越模糊,甚至可能直接在硅片上“融合”。

六、技術挑戰:HBM不是“堆上去就能跑”

HBM帶來的不僅是性能飛躍,也是一系列新的制造挑戰:

TSV可靠性與應力管理

TSV的機械應力可能引發微裂紋,導致芯片翹曲或失效。

工藝需精確控制通孔蝕刻、填充、熱循環匹配。

熱管理

多層堆疊意味著熱量更集中。HBM堆棧內部熱阻高,需要更高效的散熱通道與熱界面材料。

中介層制造復雜性與成本

硅中介層的布線精度極高,良率直接決定封裝成本。每增加一條信號線,成本幾乎線性上升。

測試與良率控制

多層堆疊帶來測試難度。任何一層失效都可能報廢整個堆棧,因此需要層級測試與Known Good Die (KGD) 策略。

七、總結:HBM,是AI算力的“隱形地基”

HBM的本質是——用三維堆疊和超密互連,把帶寬做成“面”而不是“線”。

它改變了內存與計算芯片之間的關系,從“獨立模塊”變成“緊密耦合系統”。

AI GPU、超級計算、數據中心,乃至未來的Chiplet體系,都以HBM為帶寬支撐的核心。

一句話總結:

GDDR讓GPU能跑,HBM讓GPU能“飛”。

它不是快一點的內存,而是徹底重塑了“數據流動的物理結構”。

免責聲明:本文采摘自“老虎說芯”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

粵公網安備44030002007346號

粵公網安備44030002007346號